Schneider Electric et la Funmat PRO 310 NEO

Schneider Electric optimise l'efficacité de sa production avec l'INTAMSYS FUNMAT PRO 310 NEO

Lire l’article

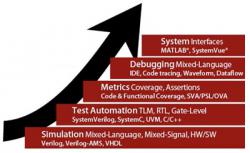

Riviera-PRO est un logiciel de simulation avancée pour FPGA et SoC compatible VHDL, Verilog, SystemC, SystemVerilog.

Le nouveau simulateur Riviera dispose d’une coeur de simulation unique (pour VHDL, Verilog, Edif, SystemVerilog / DPI, SystemC, Assertions OVA, PSL, SVA, VTL) autorisant des performances de simulation maximales, adaptées à la simulation des systèmes ASIC, SoC et gros FPGA.

Il propose de nombreuses fonctionnalités intégrées et performantes pour la vérification de couverture de faute / code / expressions, le debug rapide (advanced data flow), et également l’accélération RTL matérielle sur carte de prototypage grâce à la technologie optionnelle d’aide à la certification DO-254.

L’interface de debug est développée sur la même base que celle d’Active-HDL, avec des fonctionnalités supérieures.

Un cœur de simulation unique et des outils pour travailler plus efficacement

(Code Profiler, Couverture de code avec expressions, Gestionnaire de taches, Signal Agent, Waveform Viewer/Compare)

Les technologies ALDEC reconnues sur le marché pour leur rapidité et leur précision sont au cœur de Riviera poussées au maximum (un gain minimum x3 de version en version !)

Des performances et fonctionnalités au dessus de la concurrence pour un prix imbattable

La dernière version de Riviera apporte un nouveau noyau de simulation mixte avec le support 64 Bits natif, des performances en compilation et simulation encore meilleures (+50% en VHDL !), la possibilité de sauver et restaurer les simulations, un support complet de VHDL 2008, Verilog 2005, SystemVerilog 2009/2012, OVM/UVM, Assertions PSL, et des fonctionnalités de code coverage incluant le fameux Expression/Condition Coverage (couverture des expressions HDL), Lint et de waveforms améliorées. Vous bénéficiez également d’une toute nouvelle Interface graphique !

Question technique, info ou demande d’offre

Réservé aux professionnels